Closed-loop VDD Scaling with Canary Replicas for SRAM Standby Power Minimization

|

This project investigates circuit and architectural techniques to improve the reliability of SRAM at extreme temperatures, particularly for automotive applications. The goal is to design and implement SRAMs that are capable of monitoring and adapting their circuits and micro-architectures to very wide range changes in environmental conditions. |

|

This project explores algorithm, architectural and circuit ideas for implementation of Security Functions on RFID tags. An RFID tag harvests its power from the RF field that a reader sets-up while reading the tag. Typical power consumption, gate count and cost are below 10uW, 50K and 10 cents respectively. We explore energy efficient sub-threshold logic and memory design that can operate at sub-10uW power levels, while also delivering performance required for computationally intensive encryption algorithms. |

|

Technology scaling has made it nearly impossible to maintain SRAM bitcell stability for dense cells. In technologies below 32nm, the SRAM bitcell size has begun to rise above the area predicted by the scaling trend followed over recent technology generations. We propose a new layout for the 6T SRAM that substantially increases the lithographic friendliness of the cell. |

|

Static metrics for SRAM read and write stability do not take into account the dynamic nature of these operations. They are either pessimistic or optimistic in predicting cell failure due to the assumption of an infinite word-line (WL) pulse. In this project, we investigate TCRIT, the minimum WL pulse required for the cell to flip, as a dynamic measure of cell writability. We also explore models, both analytical and fast-simulation, that capture the statistics of dynamic margin in SRAM. |

|

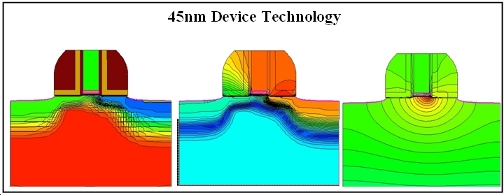

The 6T SRAM cell design has been successfully scaled in both bulk and SOI down to the 32/28nm node and has remained for more than a decade the dominant technology development vehicle for advanced CMOS technologies. Reduced device dimensions and operating voltages that accompany technology scaling have led to increased design challenges with each successive technology node. This work utilizes on a combination of TCAD and circuit simulation tools to explore the role of technology scaling on shaping the future SRAM bit cell design. In addition to random sources of variation, this work investigates the sources of non-random device mismatch in future nanoscale SRAM devices. |

|

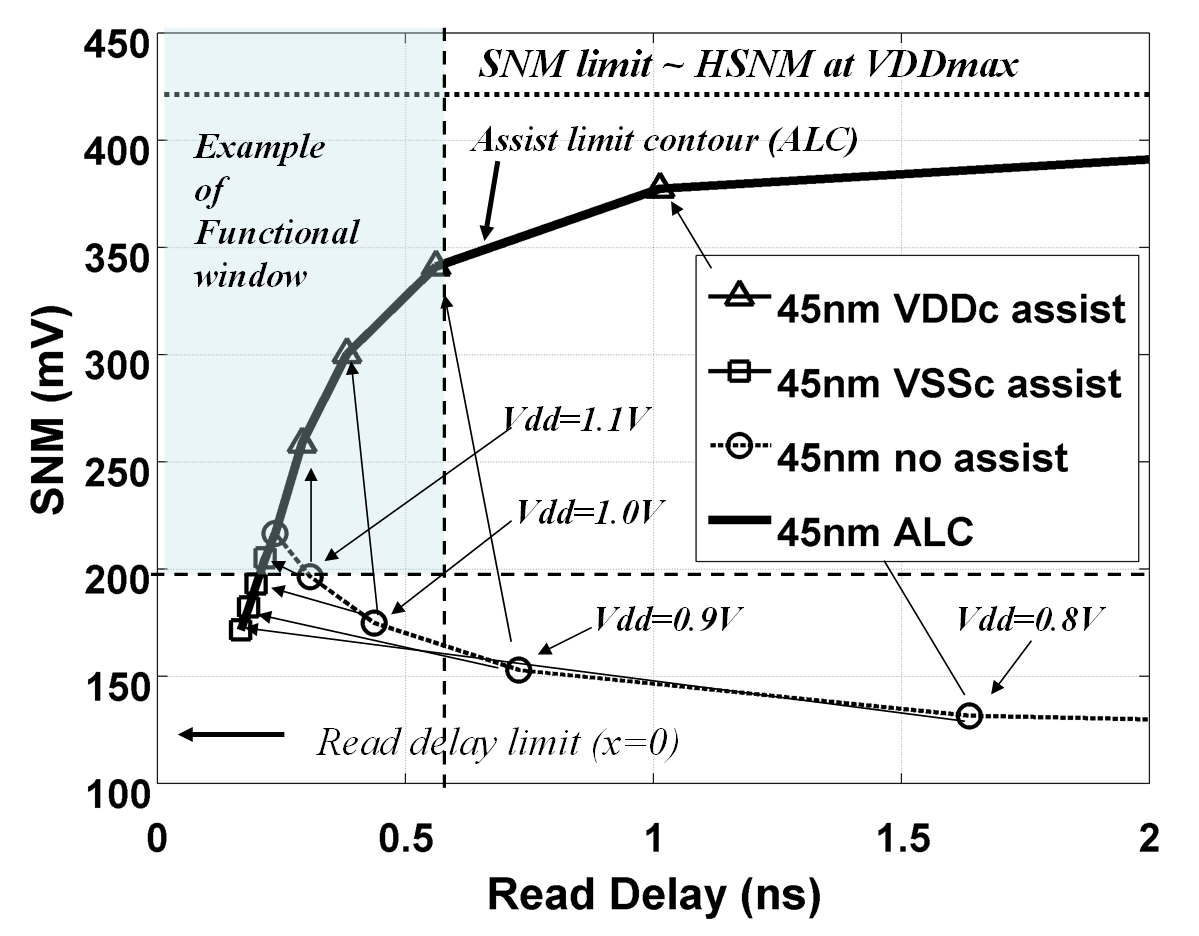

We investigate the application of these peripheral assist methods to reduce the operating voltage of SRAM, called VMIN. Lowering VMIN helps to decrease power consumption and also keeps pace with the dropping logic VDD, allowing for easier integration. Large scale 6T SRAM beyond 65nm will increasingly rely on assist methods to overcome the functional limitations associated with scaling and the inherent read stability/write margin trade off. |

|

Aggressive scaling according to Moore’s Law, combined with the push to incorporate more functionality and higher performance on a single chip, has created the widely known power problem in modern ICs. Power consumption has become a major limiting factor in many designs. A number of solutions have been preliminarily explored to help improve the energy efficiency of chips, including clock gating, power gating, local voltage regulation, and dynamic voltage scaling. While theoretical benefits of these techniques are known, their full impact on the overall power distribution network remains uncertain. This project aims to address the impact of Panoptic Dynamic Voltage Scaling (PDVS) on the power distribution network and compare them against alternative low power techniques. |

Animal research activities conducted under NMFS permit 14535 |

The artificial seal whisker project is a joint effort with the University of Virginia’s Mechanical Engineering Department and the University of California Santa Cruz to detect and track underwater wakes using an array of bio-inspired sensors. Previous biological work found harbor seals are able to track wakes using only their whiskers. In this project, the seal whisker team is focused on understanding how seals sense wakes using their whiskers, designing a capacitance based whisker-like sensor, and designing the electrical backend printed circuit board for sensing, storing, and transmitting data. The biologically inspired sensor’s design is based on seal whiskers and previous effort in the field involving spider hairs and fish lateral lines. All components will be integrated in the Wake Information Detection and Tracking System (WIDTS) to be carried by a trained harbor seal for testing. |

|

The goal of the RFID Temperature Monitor for Lab Mice is to research an efficient way to monitor the well-being of mice in a vivarium. Medical research laboratories may house very large numbers of research animals, and each animal must be visually inspected every day. In addition to being a tedious task for research personnel, visual inspection is not the most effective method for accurately assessing the well-being of the animals. This project focuses on developing an implantable RFID-like tag that allows for remote, accurate, and continuous monitoring of lab animals. |