|

We investigate the application of these peripheral assist methods to reduce the operating voltage of SRAM, called VMIN. Lowering VMIN helps to decrease power consumption and also keeps pace with the dropping logic VDD, allowing for easier integration. Large scale 6T SRAM beyond 65nm will increasingly rely on assist methods to overcome the functional limitations associated with scaling and the inherent read stability/write margin trade off. |

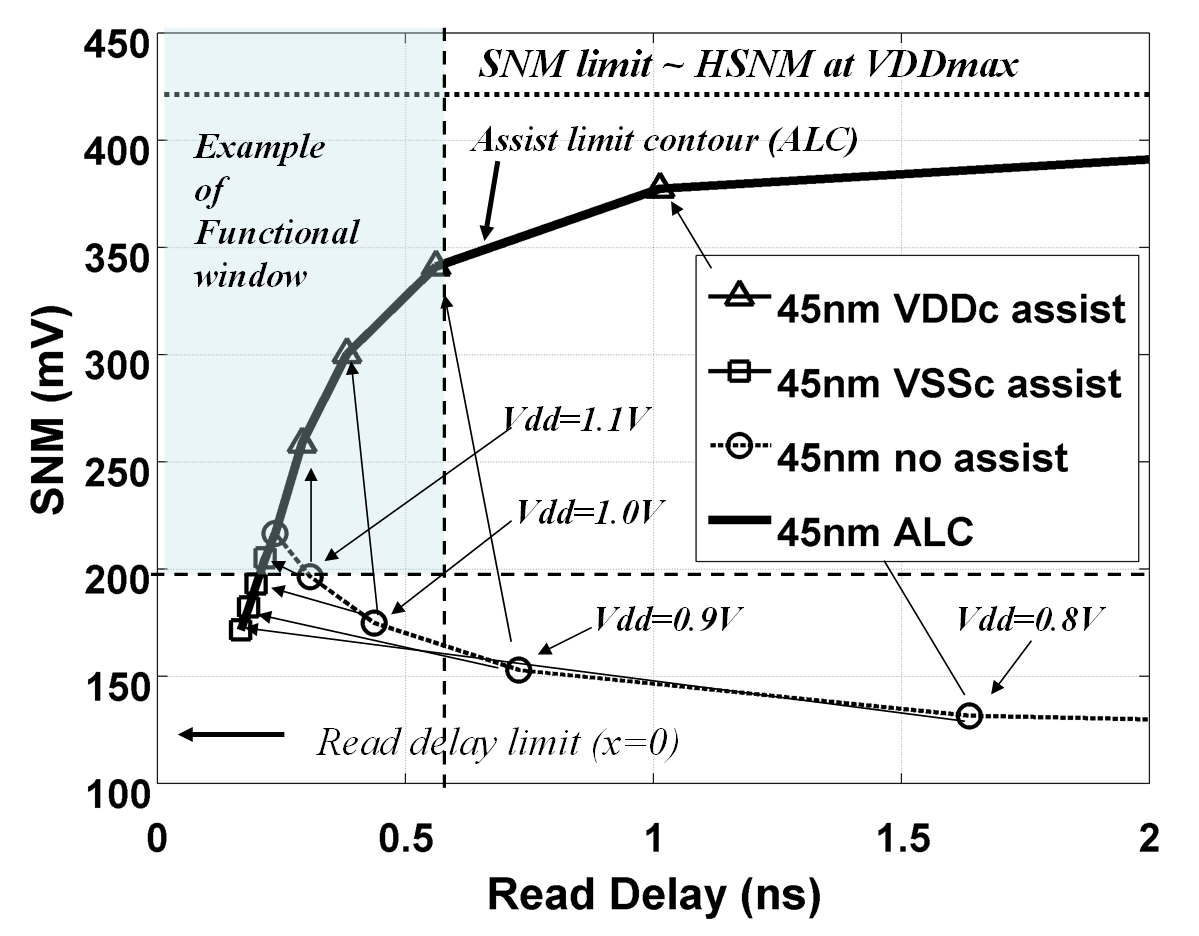

The primary focus of the circuit assist methods has been improved read or write margin with less attention given to the the implications for performance. Margin sensitivity and margin/delay analysis tools are introduced for assessing the functional effectiveness of the bias based assist methods and show the direct implications on voltage sensitive yield. A margin/delay analysis of bias based circuit assist methods is developed, highlighting the assist impact on the functional metrics, margin and performance. Assist methods are often used in conjunction with other techniques. For example, we investigate different schemes for improving sense amplifier performance in the presence of variation. In the extreme case, we also apply circuit assists (along with alternative bitcells) to support sub-threshold operation of memories. These memories can function down to 0.3V or lower, which is essential for severely energy constrained applications like Body Sensor Networks. Students Harsh Patel, Ningxi Liu, Arijit Banerjee Publications: