|

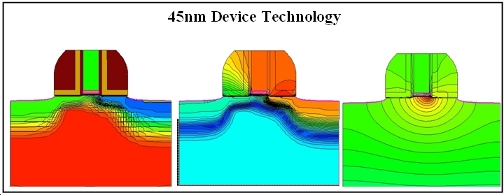

The 6T SRAM cell design has been successfully scaled in both bulk and SOI down to the 32/28nm node and has remained for more than a decade the dominant technology development vehicle for advanced CMOS technologies. Reduced device dimensions and operating voltages that accompany technology scaling have led to increased design challenges with each successive technology node. This work utilizes on a combination of TCAD and circuit simulation tools to explore the role of technology scaling on shaping the future SRAM bit cell design. In addition to random sources of variation, this work investigates the sources of non-random device mismatch in future nanoscale SRAM devices. |

Publications

Project Type: