|

This work compares six different 8T SRAM bitcells targeting different design space requirements - such as reliability and low power/energy - for Internet of Things (IoT) applications. Different bitcells leverage the varying characteristics of high threshold (high-VT) and standard-threshold (standard-VT) devices to affect SRAM metrics like write margin (WM), Data Retention Voltage (DRV), Hold Static Noise Margin (HSNM), Read Static Noise Margin (RSNM), write and read energy, standby leakage power, and variability. The reliability for each bitcell over process (intra- and inter-die variation) and temperature variation is also evaluated. Measured results for a commercial 130nm test chip compare the most promising two 8T bitcell structures targeting low leakage and low energy. |

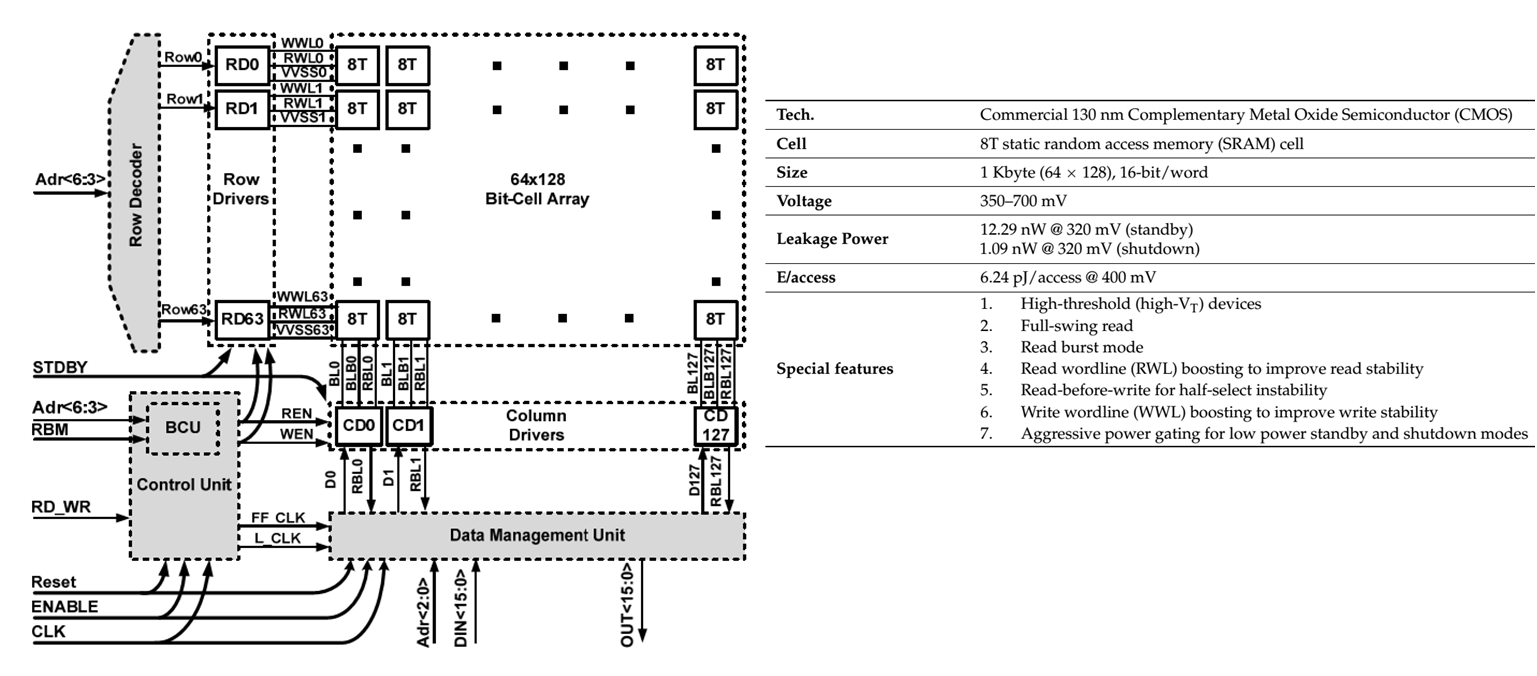

Based on previous analysis, we design an ultra-low power (ULP) 1 KB SRAM macro for Internet of Things (IoT) battery-less systems-on-chip (SoCs) operating under varying energy harvesting conditions. The unique combination of features within this array allows battery-less SoCs to retain important information for a significantly longer period of time when energy harvesting conditions are poor. The array uses 8T high-threshold (high-VT) static random access memory (SRAM) cells with word line boosting to eliminate write failures coupled with a read-before-write scheme to address read-disturb in half-selected cells.

The proposed array can operate at a wide range of supply voltages (350–700 mV) and has two ULP modes: standby with retention (1.5 pW/bit) and shutdown without retention (0.13 pW/bit). Aggressive power gating of all peripherals during the standby state reduces the array power consumption down to 12.29 nW/KB at 320 mV with data retention. Compared to previously published 8T arrays, the proposed design provides the lowest standby power. The complete shutdown of the array allows further reduction down to 1.09 nW/KB. The measured results from a commercial 130 nm chip show that the proposed array consumes a minimum of 6.24 pJ/access with a 17.16 nW standby power at 400 mV. The read burst mode allows up to 22% reduction in energy/access at 400 mV.