|

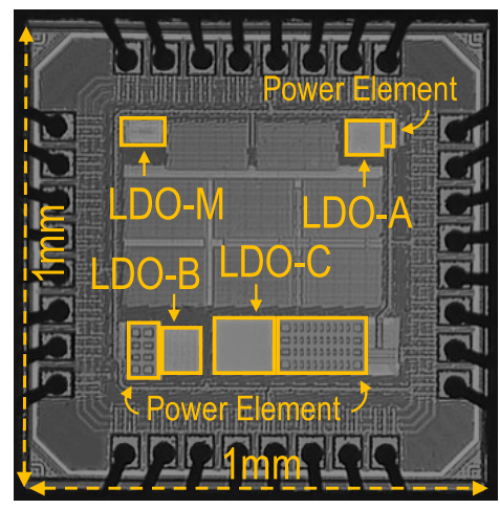

The design and verification process for analog circuits can be long and tedious, wherein designers rely heavily on manual effort to create circuits and draw layouts, thereby limiting turn-around-time and design scale and increasing costs. Various previous works have tried to solve this issue by leveraging digital automated place-and-route (APR) tools, but they involve replacing analog elements with digital counterparts, thereby dampening performance. In this work, we propose a digital flow-based approach to design all-analog circuits that dramatically speeds up the design and layout process while retaining the benefits of true analog topologies and demonstrate the performance for three low-dropout regulators (LDOs). Fabricated in 65-nm CMOS, measurement results show that the generated LDOs achieve up to 99.95% peak current efficiency, a figure-of-merit (FOM) of 4.6 ps, and up to 63.93% reduction in input offset variability with respect to their manually designed counterparts. |